## TRANSFORMER COUPLED HIGH-DENSITY CIRCUIT TECHNIQUE FOR MMIC

D. Ferguson, P. Bauhahn, J. Keuper, R. Lokken,

J. Culp, C. Chao, A. Podell\*

Honeywell Inc., Minneapolis, Minnesota 55440

### ABSTRACT

A circuit technique that employs a transformer wrapped around an active device to increase circuit density has been demonstrated with key building blocks for sensor systems. This technique is completely compatible with planar fabrication processes used in the fabrication of high-density and high-yield circuits. Measured results from a wraparound transformer-FET combination are compared with a similar circuit that incorporates octagonal transformers. The wraparound technique has been successfully implemented in the design of a transmitter and an image reject mixer. Test results from these circuits are presented.

### INTRODUCTION

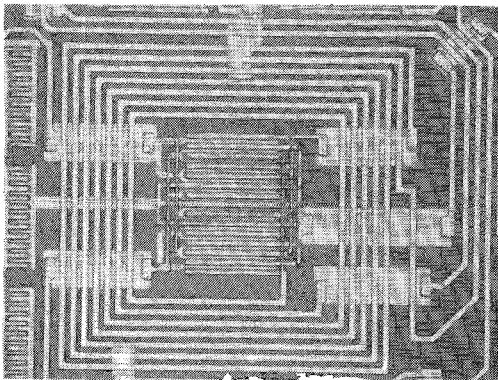

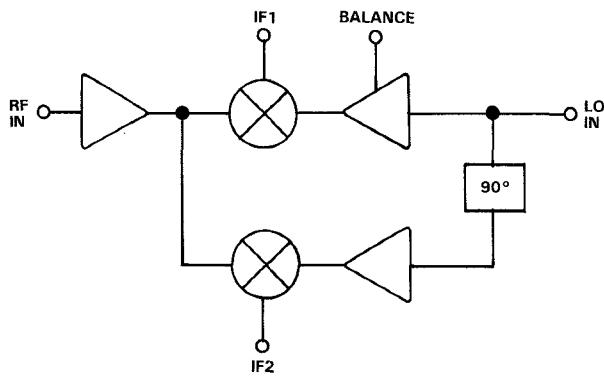

Planar inductors are broadly accepted as a means of matching and providing bias in monolithic microwave integrated circuits (MMIC). This paper describes a technique of interstage coupling that accomplishes these functions based on two interwound square inductors that encircle an active device as shown in Figure 1. The inductors form an interstage transformer and are completely compatible with low cost and high-yield fabrication processes. This technique requires 20% less area than the octagonal transformer coupling previously reported<sup>1</sup>. The wraparound transformer technique has been successfully

Figure 1. Wrap Around Transformer and

Balanced FET

demonstrated with the development of a single stage amplifier, an image reject mixer, and a transmitter. To our knowledge, the circuits reported here are the most complex monolithic analog circuits achieved at these frequencies.

### DESIGN

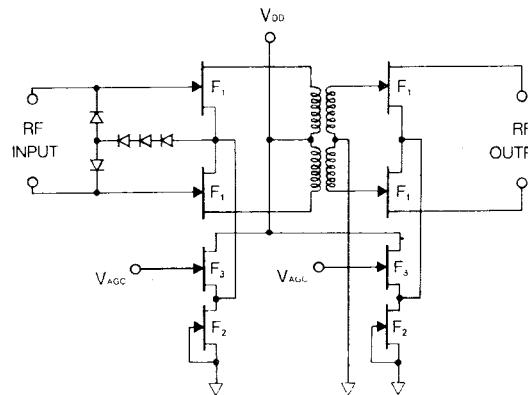

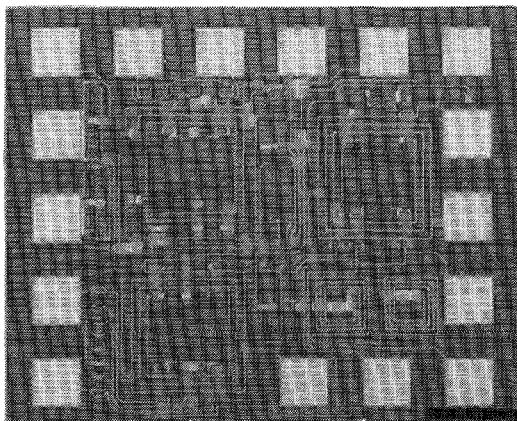

The performance of the wraparound transformer was evaluated by measuring the characteristics of the amplifier shown in Figure 2, implemented

Figure 2. Transformer Test Circuit

with both wraparound and octagonal transformers. With the exception of the transformers, the designs were identical. The inductance of the transformer secondary was selected to resonate with the input capacitance of the next stage FET. The transformers were designed with three micron line/space layout rules and the coupling was approximately 1:1. The active devices were common source MESFETs that were biased at 18% IDSS for low noise by F<sub>2</sub>. The AGC function was implemented with the addition of a second FET F<sub>3</sub> that subtracts bias current from the amplifier in response to an AGC control voltage.

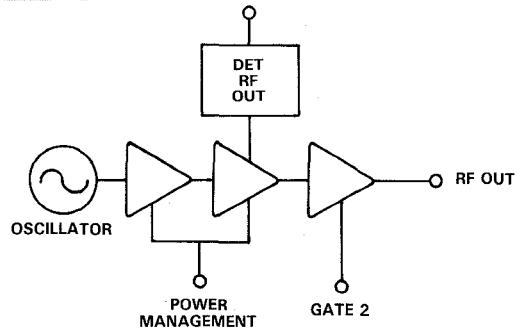

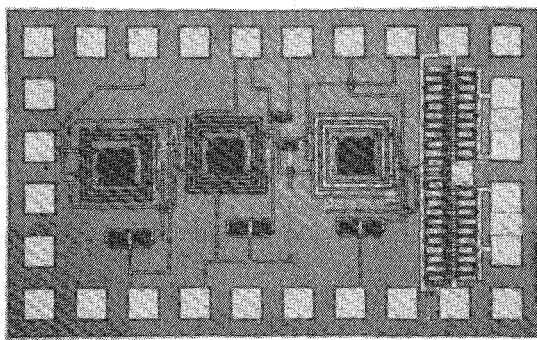

The wraparound transformer technique was used exclusively for interstage coupling in the transmitter circuit shown in Figure 3, and the image reject mixer (IRM) shown in Figure 4. The transmitter consists of an oscillator, two amplifier stages, and a power amplifier. The amplifier stages provide gain to saturate the

Figure 3. Monolithic Transmitter.

Chip Size is 1 x 1.5 mm

Figure 4. Monolithic Image Reject Mixer.

Chip Size is 0.7 x 1 mm

1000 micron dual-gate FETs in the power amplifier. Bias FETs are included for all of the stages except the power amplifier which must be biased externally.

The image reject mixer consists of a single stage of RF gain, two LO buffer amplifiers, a fixed 90° phase shift, and two double balanced mixers. The mixers are driven with RF signals that are in phase and LO signals which are in quadrature. The optimum image cancellation is achieved by adjusting the gain of the LO buffer amplifier to balance the mixers.

#### FABRICATION

All circuits were fabricated on a 20 mil semi-insulating GaAs substrate. FET active channels were formed by selective implantation of selenium to give a  $V_T$  of -2.7 volts. FET contact regions were implanted with sulfur. MoAuPt was used for gate level metalization and dielectric assisted liftoff was used to improve the yield. The interlevel dielectric was silicon oxy-nitride deposited by plasma enhanced CVD. The second level metal consisted of TiWAl sputtered to a thickness of 1.5 microns and patterned by ion milling.

#### RESULTS

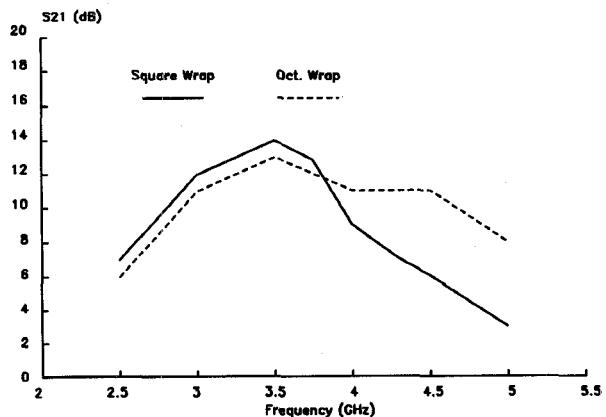

The circuits were evaluated in an RF test fixture that incorporated wideband baluns and replaceable alumina chip carriers. Figure 5 shows frequency response of the amplifier circuit with the wraparound and octagonal transformers. Both amplifiers were fabricated on the same wafer. The supply voltage was 5V and the AGC input was grounded for maximum gain.

Figure 5. Comparison of Circuit Gain with Square Wrapped and Octagonal Transformers

Both wraparound and octagonal circuits had maximum gain at 3.5 GHz. The gain of the wraparound circuit was 1 dB higher at 3.5 GHz and 2 dB lower from 4 to 5 GHz.

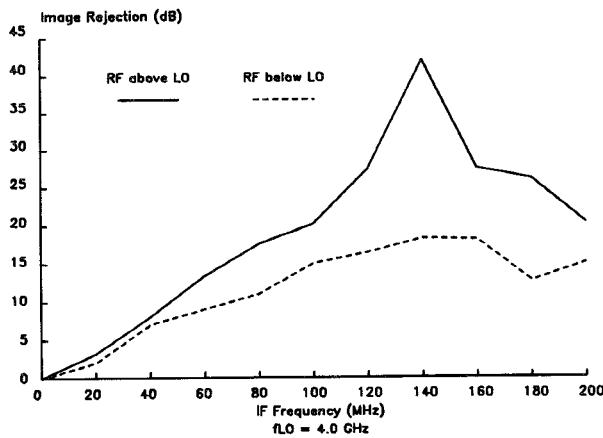

Figure 6 shows the performance of the image reject mixer. The supply voltage was 5V and the balance voltage was adjusted in each case to achieve best image rejection. The LO frequency was 4 GHz, the IF hybrid band was 120-180 MHz, and the RF input was varied above and below the local oscillator. Image rejection of greater than 25 dB was achieved over an RF input from 4.12 to 4.18 GHz with a maximum of 42 dB at 4.14 GHz. The measured conversion loss of 10 dB was consistent with the circuit loss budget.

Figure 6. Image Rejection of Monolithic Mixer

The transmitter characteristics were measured with a 5V supply for the oscillator/interstage amplifiers and a 5.5V supply for the dual gate output FETs. Bias voltages to the output FET

were adjusted for an optimum current. Measured output power of 240mW exceeded the design goal of 200mW. The transmitter efficiency biased for CW operation was 9.6%. The oscillator was locked to a dielectric resonator and tuning was accomplished by adjusting the spacing between the resonator and ground. The best pulse performance was obtained when the supply voltages were modulated with the appropriate pulse waveform. Risetimes of one nanosecond were measured on pulsedwidths as narrow as 15 nanoseconds.

#### CONCLUSIONS

A transmitter and image reject mixer that incorporated the wraparound transformers have been built and demonstrated. The wraparound transformer offers a technique for fabricating very compact gain stages. The technique is comparable in performance and requires 20% less area than an equivalent gain stage using octagonal transformers.

#### ACKNOWLEDGEMENTS

We would like to acknowledge M. Tutt and P. Schwab for fabrication, packaging, and testing of the devices.

#### REFERENCES

- (1) S.A. Jamison, et.al., "Inductively Coupled Push-Pull Amplifiers for Low Cost Monolithic Microwave ICs", 1982 GaAs IC Symposium, Phoenix, AZ.

\*This author is with Podell Associates, Palo Alto, California.